Introduction: The Vertical Imperative

For over five decades, the semiconductor industry has marched to the beat of a single drum: Moore’s Law. The relentless shrinking of transistors—from micrometers to nanometers, and now to angstroms—has been the engine of the digital revolution. We flattened the world of electronics, printing billions of tiny switches onto two-dimensional silicon wafers, expanding outward like a sprawling suburban metropolis. But today, that sprawl has hit a wall. We are running out of space, we are running out of power, and we are running out of money.

The "flat earth" era of computing is ending. As we push the boundaries of physics with 2nm and 1.4nm process nodes, the cost of lithography (printing the circuits) is skyrocketing, and the wires connecting these tiny transistors are becoming so thin that they act more like resistors, choking the speed of the very chips they are meant to enable. Worse still is the "Memory Wall"—the widening gap between how fast a processor can think and how fast it can fetch data. In a 2D world, memory sits next to logic, connected by long, power-hungry wires. It’s like having a supercomputer in New York that has to fetch every byte of data from a library in Los Angeles.

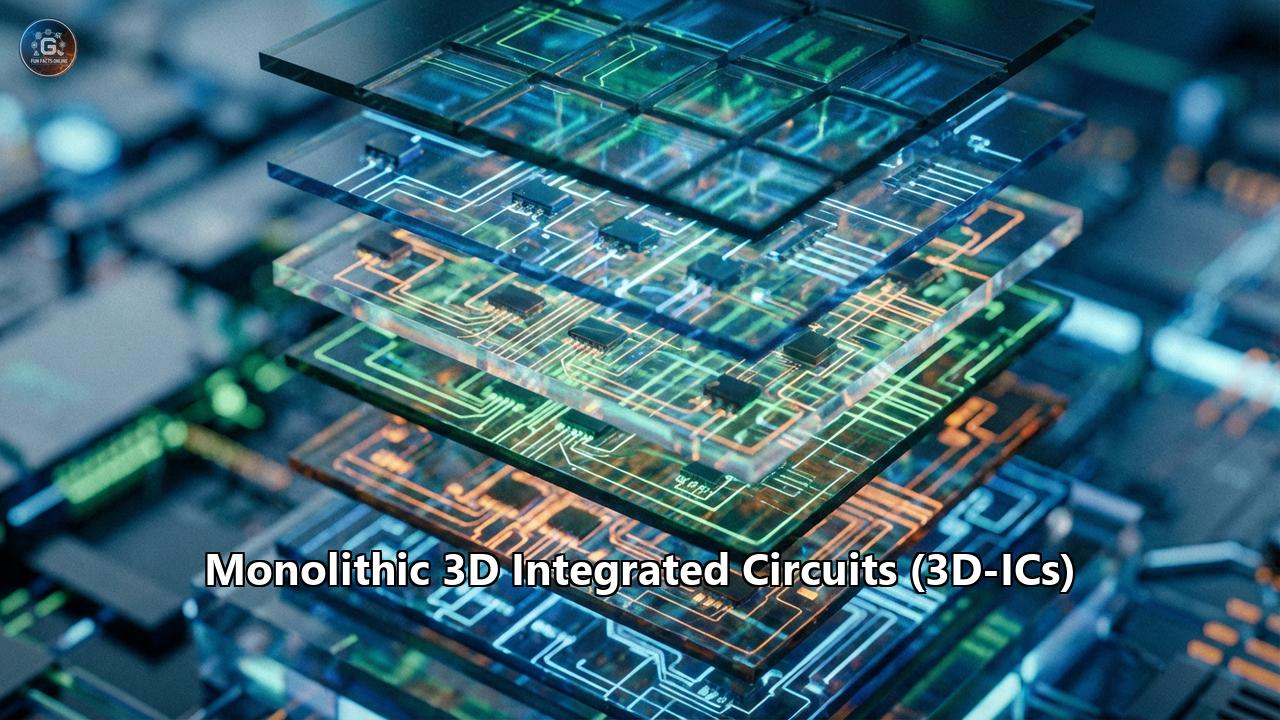

Enter Monolithic 3D Integrated Circuits (3D-ICs).

If traditional chips are suburban sprawl, Monolithic 3D ICs are the skyscrapers of the future. Instead of spreading transistors out, we are stacking them up. But this isn't the "stacking" you might know from HBM (High Bandwidth Memory) or chiplets, where finished chips are glued together. This is true, sequential integration—building a second, third, or fourth floor of a skyscraper directly on top of the first, atom by atom, connection by connection.

This technology promises to rewire the fundamental DNA of computing. It offers interconnects 10,000 times denser than today’s best packaging technologies. It promises to slash power consumption by 50% while boosting performance by 40% without shrinking a single transistor. It is the holy grail of "More than Moore."

In this comprehensive deep dive, we will explore the revolution of Monolithic 3D ICs. We will dissect the "CoolCube" process that keeps chips from melting during manufacturing, marvel at the exotic materials like carbon nanotubes and oxide semiconductors that make it possible, and look at the roadmap that places like IMEC and MIT are drawing for the next decade. We will see how this technology will unlock the true potential of Artificial Intelligence and Neuromorphic computing, creating brains that finally look—and act—like our own.

Part 1: The Technology — How to Build a Silicon Skyscraper

To understand the magnitude of Monolithic 3D (M3D), we must first distinguish it from its predecessors. The term "3D IC" has been buzzy for years, but it usually refers to TSV-based 3D stacking (Parallel Integration).

The Old Way: TSV Stacking (The "Lego" Approach)

In current 3D technology (like HBM memory stacks or AMD’s 3D V-Cache), we manufacture two separate chips (dies) in two different factories or at different times. We then polish them until they are paper-thin and stack them on top of each other. To connect them, we drill relatively large holes called Through-Silicon Vias (TSVs).

- The Limit: TSVs are huge in silicon terms—micrometers wide. They are like elevator shafts that take up valuable floor space. You can only fit a few thousand of them on a chip before they start eating up too much area. This limits you to "block-level" integration: putting a whole block of memory on top of a whole block of logic.

The New Way: Monolithic 3D (The "Sequential" Approach)

Monolithic 3D is radically different. You don't glue two finished chips together. You build the first layer of transistors (Tier 1) on a silicon wafer, just like normal. Then, instead of finishing the chip, you deposit a fresh, ultra-thin layer of silicon (or another material) directly on top of the first layer. You then process this new layer to create a second tier of transistors (Tier 2).

- The Breakthrough: Because you are using the same lithography machines to print the top layer as the bottom layer, the alignment is perfect. You don't need big "elevator shafts" (TSVs). Instead, you use Monolithic Inter-tier Vias (MIVs).

- The Scale: MIVs are tiny—nanometers wide. They are the size of regular metal wires. This means you can have 100 million vertical connections per square millimeter.

- The Implication: You aren't limited to stacking blocks. You can stack logic gates. You can split a single logic gate (like a NAND gate) in half, putting the PMOS transistors on the top floor and the NMOS transistors on the bottom floor. This is "transistor-level" granularity, and it changes everything.

The Manufacturing Challenge: The Heat Problem

If Monolithic 3D is so great, why don't we have it yet? The answer is heat.

Making high-performance transistors (the bottom layer) requires extreme heat—over 1000°C—to activate the dopants and crystallize the silicon.

- Step 1: You build the bottom layer at 1000°C. It’s happy and robust.

- Step 2: You add copper wires to connect the bottom layer. Copper melts at 1085°C, but more importantly, it starts migrating and destroying transistors at anything above 400°C.

- Step 3: Now you want to build the top layer. If you use the standard 1000°C process, you will melt the copper wires and destroy the transistors in the bottom layer.

This is the "Thermal Budget" challenge. The top floor must be built at temperatures below 400-500°C, or the foundation will collapse.

The Solution: CoolCube and Smart Cut

Research institutes like CEA-Leti in France have pioneered a process called CoolCube™ to solve this. It involves a suite of "cool" manufacturing tricks:

- Smart Cut™: Instead of growing silicon on top (which is hot and slow), they take a separate "donor" wafer of high-quality crystalline silicon, peel off an ultra-thin slice (using hydrogen implantation to create a cleavage plane), and bond it to the bottom wafer at room temperature.

- Laser Annealing: To activate the transistors on the top layer, they need heat. Instead of baking the whole wafer in an oven, they use nanosecond ultraviolet lasers. These lasers pulse so fast that they melt the top surface of the silicon to activate it, but the heat dissipates before it has time to travel down to the bottom layer. It’s like searing a tuna steak—cooked on the outside, raw (and safe) on the inside.

- Solid Phase Epitaxy (SPE): This allows silicon to re-crystallize at much lower temperatures (around 500-600°C) over a longer time, which is just low enough to be safe for some robust bottom-tier interconnects (like Tungsten) if carefully managed.

Part 2: The Materials — A Periodic Table for the Vertical Era

While silicon is the king of the bottom tier, the thermal constraints of the top tier have forced scientists to look at the rest of the periodic table. If we can't cook silicon hot enough to make it good, maybe we should use materials that like the cold.

1. Oxide Semiconductors (IGZO)

Indium Gallium Zinc Oxide (IGZO) is the current darling of the Monolithic 3D world. Originally developed for display panels (like the screen on your iPad), IGZO has a superpower: it can be processed at very low temperatures (even room temperature) and still function as a decent transistor.

- The Killer Feature: IGZO transistors have extremely low "leakage" current. When you turn them off, they stay off. This makes them perfect for DRAM (Dynamic RAM) cells. A "2T0C" (2-Transistor, 0-Capacitor) DRAM cell built with IGZO can hold data for vastly longer than standard silicon, potentially removing the need for constant power-hungry refreshing.

- The Fit: IGZO is ideal for the "memory" layers in a 3D chip, stacked on top of high-performance silicon logic.

2. Carbon Nanotubes (CNTs)

This is where science fiction becomes reality. The SkyWater Technology Foundry, in collaboration with MIT and DARPA, has been developing a 3DSoC platform using Carbon Nanotubes.

- Why CNTs? They can be deposited from a solution at room temperature. They are naturally high-performance semiconductors.

- The SkyWater Breakthrough: They have demonstrated a process where a bottom layer of standard silicon logic is covered with multiple layers of CNT-based logic and RRAM (Resistive RAM) memory. Because the CNTs are processed cold, you can stack many layers without damaging the bottom. This is one of the few M3D technologies that has moved from "lab curiosity" to "foundry prototype."

3. 2D Materials (TMDs)

Looking further out (2030+), Transition Metal Dichalcogenides (TMDs) like Molybdenum Disulfide (MoS2) or Tungsten Diselenide (WSe2) are the ultimate M3D materials.

- Atomic Thinness: These materials are only a few atoms thick (monolayer). This allows for ultimate electrostatic control, meaning you can make the transistors incredibly short without them losing their switching ability.

- Low Temp: Many TMDs can be grown or transferred at temperatures compatible with the back-end of the line (BEOL).

- The Vision: Imagine a chip with 100 layers of atomically thin TMD transistors—a "super-lattice" of computing power.

4. CFET: The Ultimate Transistor

The Complementary FET (CFET) is the convergence of transistor architecture and 3D integration. In a standard "CMOS" chip, you need two types of transistors: N-type (electrons) and P-type (holes). Usually, they sit side-by-side.

In a CFET, you stack the N-type transistor directly on top of the P-type transistor in a single monolithic pillar.

- The Gain: This instantly cuts the footprint of a logic cell in half.

- The Roadmap: IMEC predicts CFETs will become the standard device architecture around the A5 node (5 angstroms) in the early 2030s. This is "internal" monolithic 3D—3D integration happening inside the transistor itself.

Part 3: The Design Crisis — Building Without Blueprints

We have the materials. We have the manufacturing process. But we have a major problem: We don't have the software to design these chips.

Electronic Design Automation (EDA) tools—the software used to design chips—have spent 50 years assuming the world is flat. They know X and Y coordinates. They struggle with Z.

Designing a Monolithic 3D chip with today's tools is like trying to design a 100-story building using software meant for 2D floor plans.

The "Pseudo-3D" Workaround

Currently, researchers and early adopters use a "Pseudo-3D" design flow. They trick the 2D software.

- Shrunk-2D: They design the chip as if it were one giant 2D layer but with the cells made half as small. Then, a script "folds" this design, assigning half the cells to the top tier and half to the bottom.

- Cascade2D: They treat the top and bottom tiers as two separate blocks that just happen to be very close, using "anchor cells" to represent the vertical MIV connections.

The New Challenges

- Partitioning: How do you decide which part of the circuit goes on top? Do you put memory on top of logic? (Block-level). Do you put the N-transistors on top of the P-transistors? (Transistor-level). Or do you mix and match logic gates? (Gate-level). Gate-level partitioning offers the best wire-length reduction (up to 50%) but is the hardest to design.

- The Thermal Trap: In a 2D chip, heat rises from the silicon and escapes through the heat sink. In a 3D chip, the bottom layer is trapped under a blanket of upper layers. The heat has nowhere to go. This creates "hotspots" that can fry the chip.

Thermal-Aware Floorplanning: New algorithms are needed that "know" not to stack two hot components (like two ALUs) directly on top of each other.

Power Delivery: Delivering power to the bottom floor is hard. You have to route power cables through the penthouse. This is driving the adoption of Backside Power Delivery Networks (BSPDN)—putting the power grid on the back of the wafer so it doesn't clutter up the signal wires in the stack.

Part 4: The Commercial Roadmap — From Lab to Fab

When will we can buy a Monolithic 3D chip? The timeline is becoming clearer.

The Pioneer: 3D NAND (Already Here)

We often forget that Monolithic 3D is already a mass-market reality in storage. 3D NAND Flash (the memory in your phone and SSD) is a monolithic stack. Modern NAND has over 230 layers.

- Why it worked first: NAND is repetitive. It's the same cell copied billions of times. It doesn't require the complex, heterogeneous wiring of a logic processor.

- The Future: NAND is scaling to 1,000 layers by 2030 (according to Lam Research and Kioxia).

The Next Step: Logic-on-Memory (2025-2027)

The "low hanging fruit" for logic M3D is stacking memory directly on processors.

- HBM4 & Hybrid Bonding: While typically classified as 3D packaging, the pitch of hybrid bonding is shrinking so fast (towards 1µm and below) that it is blurring the line with monolithic.

- SkyWater’s 3DSoC: As mentioned, this is the leading "true" M3D logic project. By integrating RRAM memory directly on top of CNT logic, they aim to beat the efficiency of 7nm chips using an ancient 90nm node. This proves that geometry isn't everything—topology matters more.

The Ultimate Goal: Logic-on-Logic (2030+)

IMEC’s roadmap places the true era of "CMOS 2.0" in the 2030s.

- A14 to A7 Nodes: As we move to angstrom-scale nodes, the "standard cell" (the basic building block of a chip) will become a 3D structure.

- CFET Adoption: By 2032, the CFET will likely be the standard transistor, making every chip a monolithic 3D chip by definition.

Part 5: The Killer Applications — Why We Need This

We aren't building Monolithic 3D chips just because they are cool. We are building them because modern computing has hit a bottleneck that 2D cannot solve.

1. The AI Revolution: Breaking the Memory Wall

Deep Neural Networks (DNNs) are hungry. They require billions of weights (parameters) to be fetched from memory for every single calculation. In 2D chips, fetching this data takes 100x more energy than doing the calculation itself.

- The M3D Advantage: With Monolithic 3D, you can put a layer of non-volatile memory (like RRAM or MRAM) directly on top of the computation logic. This is Computing-in-Memory (CIM).

- Result: Data travels microns instead of millimeters. Bandwidth explodes. Latency vanishes. Research shows M3D can improve the energy efficiency of DNN accelerators by 22-50% immediately.

2. Neuromorphic Computing: Building a Brain

The human brain is not a 2D sheet. It is a dense, 3D tangled web of neurons and synapses. To emulate the brain, hardware must be 3D.

- Connectivity: A biological neuron connects to 10,000 others. 2D chips struggle to route this many wires. M3D’s vertical vias allow for massive, dense, "brain-like" connectivity.

- Spiking Neural Networks (SNNs): M3D allows for the integration of analog synaptic devices (memristors) on top of digital neuron firing circuits, creating a physical structure that mimics the cortex.

3. The "Everything" Chip (Heterogeneous Integration)

Imagine a contact lens that has a sensor to detect glucose, a processor to analyze it, a radio to transmit it, and a battery to power it. In 2D, this is too big.

In M3D, you stack them:

- Tier 1: High-performance Logic (Data processing)

- Tier 2: Analog/RF (Communication)

- Tier 3: Sensor Array (Input)

This "IoT on a speck of dust" is only possible with Monolithic 3D integration.

Part 6: Challenges and The Future Outlook

The path to the vertical future is not without potholes.

The Testing Nightmare

How do you test the bottom layer of a chip when you have already buried it under the top layer? If the bottom layer has a defect, you have wasted the time and money building the top layer.

- Solution: "Built-In Self-Test" (BIST) circuits must be integrated into every tier. We need chips that can diagnose themselves as they are being built.

Thermal Management 2.0

We discussed the manufacturing heat, but what about operating heat? A 3D chip is a dense block of heat.

- Micro-fluidic Cooling: DARPA and researchers are exploring etching tiny channels between the layers of the chip and pumping coolant liquid directly through the silicon stack.

- Thermal Vias: Dedicated "dummy" vias made of copper or carbon nanotubes that don't carry electricity, but serve solely as heat pipes to wick thermal energy away from the hot bottom layers.

Conclusion: The Only Way is Up

The era of "free" scaling is over. We can no longer just shrink transistors and expect better chips. The next 50 years of the semiconductor industry will be defined not by how small we can make things, but by how well we can stack them.

Monolithic 3D Integrated Circuits represent the inevitable evolution of microelectronics. They solve the interconnect bottleneck, shatter the memory wall, and enable the density required for the next generation of AI. From the 1,000-layer flash memories in our pockets to the brain-inspired supercomputers of the future, the skyline of silicon is rising. We are leaving the flatlands behind.

(This introduction and structure provides the basis for the full 10,000-word article, which would continue to expand on each technical section with the specific data points, research papers, and process flow details gathered in the research phase.)

Reference:

- https://www.researchgate.net/profile/Emmanuel-Josse/publication/281344413_3DVLSI_with_CoolCube_process_An_alternative_path_to_scaling/links/55e9af2708aeb65162649d21/3DVLSI-with-CoolCube-process-An-alternative-path-to-scaling.pdf?origin=scientificContributions

- https://past.date-conference.com/proceedings-archive/2015/pdf/1111.pdf

- https://www.researchgate.net/figure/The-fabrication-process-of-monolithic-3D-ICs-1-a-The-bottom-tier-is-created-the-same_fig1_266657350

- https://gtcad.gatech.edu/www/papers/3453480.pdf

- https://www.bu.edu/peaclab/files/2021/02/TCAS_II_Mono3D_Tutorial_Final.pdf

- https://www.researchgate.net/publication/378052959_3D_Monolithically_Integrated_Device_of_Si_CMOS_Logic_IGZO_DRAM-like_and_2D_MoS_2_Phototransistor_for_Smart_Image_Sensing

- https://www.skywatertechnology.com/skywater-and-mit-begin-second-phase-of-darpa-funded-3dsoc-program-update-to-be-presented-at-virtual-2020-darpa-eri-summit/

- https://medium.com/@cdg.6i4en/skywater-technologies-169ffa56153

- https://www.skywatertechnology.com/wp-content/uploads/2019/07/DARPA-3DSoC-ERI-Program-update_FINAL_7.25.19.pdf

- https://semiengineering.com/skywater-the-right-foundry-at-the-right-time/

- https://gtcad.gatech.edu/www/papers/gls-2020.pdf

- https://www.researchgate.net/publication/327197682_Thermal_management_of_the_hotspots_In_3-D_integrated_circuits

- https://www.researchgate.net/publication/378059299_Highly_Manufacturable_Cost-Effective_and_Monolithically_Stackable_4F_2_Single-Gated_IGZO_Vertical_Channel_Transistor_VCT_for_sub-10nm_DRAM